SERDES的通用結構是什么

本篇文章給大家分享的是有關SERDES的通用結構是什么,小編覺得挺實用的,因此分享給大家學習,希望大家閱讀完這篇文章后可以有所收獲,話不多說,跟著小編一起來看看吧。

成都創新互聯公司是一家集網站建設,東蘭企業網站建設,東蘭品牌網站建設,網站定制,東蘭網站建設報價,網絡營銷,網絡優化,東蘭網站推廣為一體的創新建站企業,幫助傳統企業提升企業形象加強企業競爭力。可充分滿足這一群體相比中小企業更為豐富、高端、多元的互聯網需求。同時我們時刻保持專業、時尚、前沿,時刻以成就客戶成長自我,堅持不斷學習、思考、沉淀、凈化自己,讓我們為更多的企業打造出實用型網站。

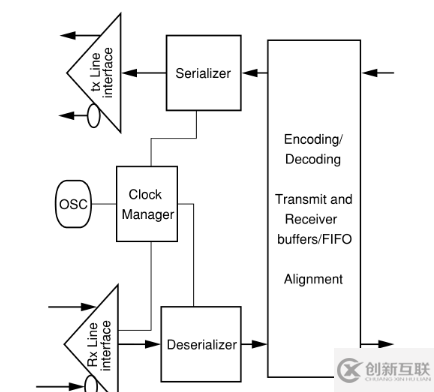

SERDES的基本構造

簡單說來,SERDES的基本框圖如下:

大概就是由發送線,接收線,串行化模塊核解串行化模塊,時鐘管理模塊,編碼解碼模塊,發射接收緩沖模塊(FIFO)以及Alignment模塊。其實還有一個由用戶根據接口協議的具體內容而自定制的用戶邏輯模塊,用來產生發送數據以及解析接收數據,這是唯一用戶可以靈活處理的地方,也是邏輯工程師可以進行電路設計(Verilog設計)的地方。

其中,發送線即圖中tx Line interface以及接收線(Rx Line Interface)是與外部芯片進行交互的串行線路,具體可以分別由一對或者多對差分信號線組成。一般而言,1對稱之為X1模式,2對X2,以此類推,n對即Xn。這類差分信號線越多,傳輸數據的帶寬就越大,假如一對差分信號線的傳輸帶寬為3.125Gbps,則n對為n*3.125Gbps。

串行化模塊(Serializer)即并串轉換(PISO)模塊,用戶邏輯產生待發送數據,經過8B/10B編碼或者其他類型的編碼,加擾,進入緩沖區等待操作,最終經過并串轉換模塊,轉換成串行數據通過發送線發送出去。同理,解串行化模塊(Deserializer)是串行化模塊的逆過程,就是將串行差分線接收的串行數據經過串并轉換(SIPO)模塊轉換為并行數據,之后經過解碼,解擾,等操作后的并行數據,交給用戶接口,用戶進行對該并行數據進行解析。

為什么會有上圖中的Transmit and Receiver buffers/FIFO呢?

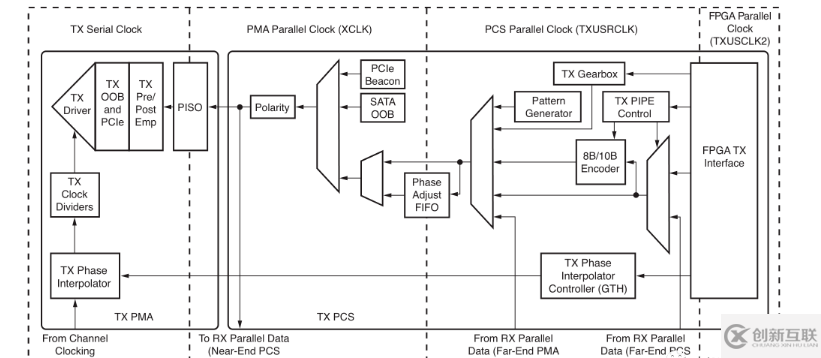

該模塊的一個最重要的作用就是進行跨時鐘域轉換!由于SERDES中涉及的時鐘不只有一個,拿我們的Xilinx的Transceiver的一個通道的發射部分而言,如下圖:

可以暫時不用管其他部分,關于Xilinx家的Transceiver,后續文章我會專門介紹。我們僅僅看它的時鐘域劃分就知道,為什么存在跨時鐘域處理這回事了。上圖中的Phase Adjust FIFO的作用就是通用SERDES中的Transmit and Receiver Buffers/FIFO的具體設計,解決的問題就是要在兩個時鐘域之間傳輸數據,必須進行速率匹配,并且要解決兩個時鐘域之間的所有相位差,簡單來說,就是跨時鐘域處理。跨時鐘域處理中,FIFO是兩個不同時鐘域之間數據傳輸的最常用的處理方式,這無論在什么時候都是筆試面試的重點,我在學生時期準備過相關的內容,見:

FPGA基礎知識極簡教程(7)詳解亞穩態與跨時鐘域傳輸

至于時鐘管理模塊,那就很明顯了,它管理了各種時鐘的問題,包括時鐘分頻倍頻以及時鐘恢復等。

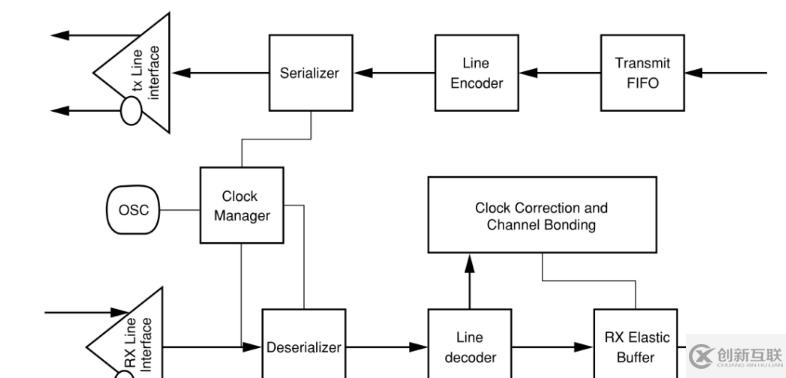

上面對SERDES的一般架構進行了簡單的口述,好像沒什么條理,下面給出一個通用的SERDES框圖,并對各模塊進行簡單定義。

SERDES的通用框圖

如下圖,為SERDES的通用框圖,它是對上一節中的SERDES框圖的一個細化。下面給出各個模塊的定義。

串行器(Serializer):獲取n位并行數據,其速率為y,然后將它轉化為串行數據流,速率為y的n倍; 解串器(Deserializer):以n的y的速率獲取串行數據流,并將其轉換為速率為y的寬度為n的并行數據; 接收對齊(Rx (Receive) Align):Rx(接收)對齊:將輸入的數據對齊到適當的字界。可以使用幾種不同的機制,從自動檢測和對齊一個特殊的保留位序列(通常稱為Comma)到用戶控制的位滑移; 時鐘管理器(Clock Manager):管理各種時鐘需求,包括時鐘倍頻,時鐘分頻和時鐘恢復; 發送FIFO(Transmit FIFO):允許在發送之前存儲傳入的用戶數據; 接收FIFO(Receive FIFO):允許在刪除之前存儲接收到的數據(緩存數據);在需要時鐘校正的系統中至關重要; 接收線接口:模擬接收電路包括差分接收器,并且可以包括有源或無源均衡; 發送線接口:模擬發射電路通常允許不同的驅動強度。它還可以允許預加重發射; Line Encoder:將數據編碼為更友好的數據格式。這通常涉及消除長序列的不變位。可能還會調整數據,以實現一平衡和零平衡。(這是一個可選塊,有時不包含在SERDES中。); 線路解碼器:從線路編碼數據解碼為純數據。(這是一個可選塊,有時在SERDES之外完成。); 時鐘校正和通道綁定:允許校正發送時鐘和接收時鐘之間的差異。還允許在多個通道之間進行偏斜校正。(通道綁定是可選的,并不總是包含在SERDES中。)

可以包括其他可能的功能,例如循環冗余校驗(CRC)生成器,CRC檢查器,4b / 5b,8b / 10b,64b / 66b的多種編碼和解碼,可設置的加擾器,各種對齊方式和菊花鏈選項以及可配置時鐘的前端和后端。

市場上的SERDES或Transceiver展示

下面列舉了兩家的吉比特收發器的架構,但本文暫時不做具體解釋,具體內容會在本系列的后面介紹。

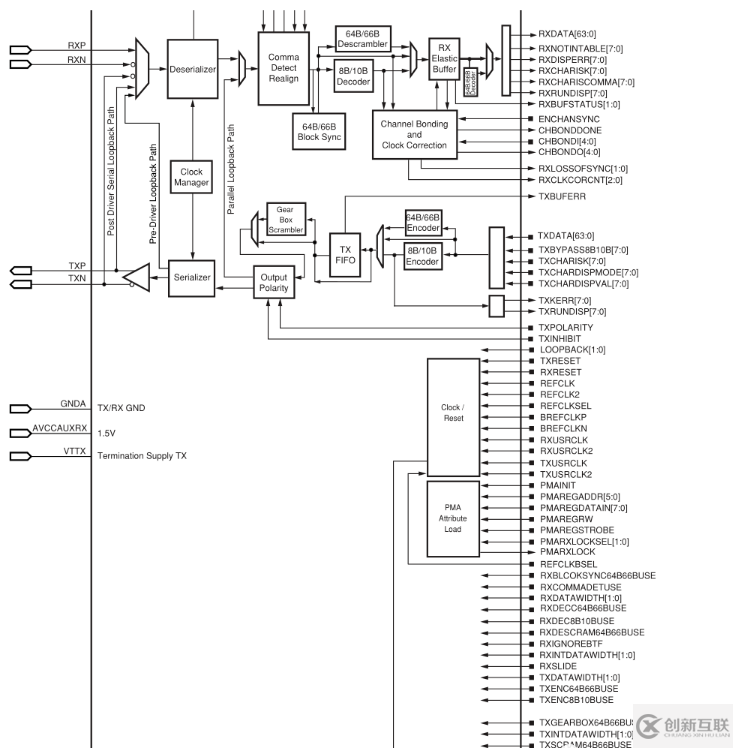

Xilinx的Transceiver架構展示

為了簡化瀏覽,我們僅僅給出一個通道的Transceiver的結構(7系列FPGA為例):

Altera的SERDES介紹

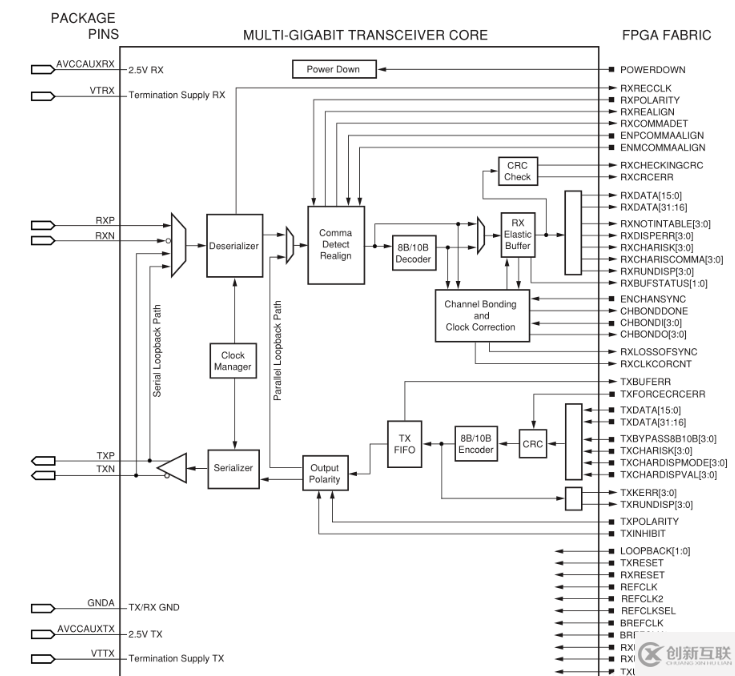

Virtex?-II Pro X RocketIO? SERDES結構框圖:

Virtex-II Pro RocketIO SERDES結構框圖:

以上就是SERDES的通用結構是什么,小編相信有部分知識點可能是我們日常工作會見到或用到的。希望你能通過這篇文章學到更多知識。更多詳情敬請關注創新互聯行業資訊頻道。

本文名稱:SERDES的通用結構是什么

當前地址:http://www.2m8n56k.cn/article18/gposgp.html

成都網站建設公司_創新互聯,為您提供網頁設計公司、全網營銷推廣、品牌網站建設、App開發、網站策劃、網站設計

聲明:本網站發布的內容(圖片、視頻和文字)以用戶投稿、用戶轉載內容為主,如果涉及侵權請盡快告知,我們將會在第一時間刪除。文章觀點不代表本網站立場,如需處理請聯系客服。電話:028-86922220;郵箱:[email protected]。內容未經允許不得轉載,或轉載時需注明來源: 創新互聯

- 企業網站制作方案應該注意什么? 2023-01-21

- 企業網站制作容易被忽視的五大素 2022-08-12

- 企業網站制作過程中客戶的基本需求有哪些? 2016-05-22

- 深圳創新互聯建議給中小企業網站制作的幾個建議 2022-06-23

- 成都企業網站制作需要多長時間_成都網站建設創新互聯科技 2021-11-16

- 網絡大潮下企業網站制作與托管的意義 2021-07-18

- 企業網站制作前需策劃的網站后臺功能 2021-06-15

- 如何增強企業網站制作效果兩手抓兩手都要硬 2021-11-10

- 成都網站建設談企業網站制作都有哪些收費項目? 2016-10-14

- 企業網站制作為什么要對用戶友好? 2023-03-31

- 遵義企業網站制作:PHP和JaVE有哪些不同呢? 2021-12-06

- 關于企業網站制作建設的發展建議 2022-06-19